MPRPPCPRG-01 MPCPRG/D

10/95

PowerPC

Microprocessor Family:

The Programmer’s Reference Guide

Motorola Inc. 1995

Portions hereof

International Business Machines Corp. 1991–1995. All rights reserved.

This document contains information on a new product under development by Motorola and IBM. Motorola and IBM reserve the right to change or

discontinue this product without notice. Information in this document is provided solely to enable system and software implementers to use PowerPC

microprocessors. There are no express or implied copyright or patent licenses granted hereunder by Motorola or IBM to design, modify the design of, or

fabricate circuits based on the information in this document.

The PowerPC 60x microprocessors embody the intellectual property of Motorola and of IBM. However, neither Motorola nor IBM assumes any

responsibility or liability as to any aspects of the performance, operation, or other attributes of the microprocessor as marketed by the other party or by

any third party. Neither Motorola nor IBM is to be considered an agent or representative of the other, and neither has assumed, created, or granted hereby

any right or authority to the other, or to any third party, to assume or create any express or implied obligations on its behalf. Information such as data

sheets, as well as sales terms and conditions such as prices, schedules, and support, for the product may vary as between parties selling the product.

Accordingly, customers wishing to learn more information about the products as marketed by a given party should contact that party.

Both Motorola and IBM reserve the right to modify this manual and/or any of the products as described herein without further notice.

NOTHING IN THIS

MANUAL, NOR IN ANY OF THE ERRATA SHEETS, DATA SHEETS, AND OTHER SUPPORTING DOCUMENTATION, SHALL BE INTERPRETED AS

THE CONVEYANCE BY MOTOROLA OR IBM OF AN EXPRESS WARRANTY OF ANY KIND OR IMPLIED WARRANTY, REPRESENTATION, OR

GUARANTEE REGARDING THE MERCHANTABILITY OR FITNESS OF THE PRODUCTS FOR ANY PARTICULAR PURPOSE

. Neither Motorola nor

IBM assumes any liability or obligation for damages of any kind arising out of the application or use of these materials. Any warranty or other obligations

as to the products described herein shall be undertaken solely by the marketing party to the customer, under a separate sale agreement between the

marketing party and the customer. In the absence of such an agreement, no liability is assumed by Motorola, IBM, or the marketing party for any damages,

actual or otherwise.

“Typical” parameters can and do vary in different applications. All operating parameters, including “Typicals,” must be validated for each customer

application by customer’s technical experts. Neither Motorola nor IBM convey any license under their respective intellectual property rights nor the rights

of others. Neither Motorola nor IBM makes any claim, warranty, or representation, express or implied, that the products described in this manual are

designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support

or sustain life, or for any other application in which the failure of the product could create a situation where personal injury or death may occur. Should

customer purchase or use the products for any such unintended or unauthorized application, customer shall indemnify and hold Motorola and IBM and

their respective officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable

attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such

claim alleges that Motorola or IBM was negligent regarding the design or manufacture of the part.

Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

IBM and IBM logo are registered trademarks, and IBM Microelectronics is a trademark of International Business Machines Corp.

The PowerPC name, PowerPC logotype, and PowerPC 601 are trademarks of International Business Machines Corp. used by Motorola under license

from International Business Machines Corp. International Business Machines Corp. is an Equal Opportunity/Affirmative Action Employer.

This document was created with FrameMaker 4.0.4

PowerPC Microprocessor Family: The Programmer’s Reference Guide

1

Introduction

The primary objective of this document is to provide a concise method by which system

software and hardware developers and application programmers may more readily provide

software that is compatible across the family of PowerPC processors and other devices. A

more detailed account of the following topics or the PowerPC architecture in general, may

be obtained from the

PowerPC Microprocessor Family: The Programming Environments

,

referred to as

The Programming Environments Manual

. (

The PowerPC Architecture: A

Specification for a New Family of RISC Processors

defines the architecture from the

perspective of the three programming environments and remains the defining document for

the PowerPC architecture.)

This document is divided into four parts:

• Part 1, “Register Summary,” on page 4 provides a brief overview of the PowerPC

register set, including a programming model and quick reference guides for both 32-

and 64-bit registers.

• Part 2, “Memory Control Model,” on page 28 provides a brief outline of the page

table entry and segment table entry for both 32- and 64-bit implementations.

• Part 3, “Exception Vectors,” on page 40 provides a quick reference for exception

types and the conditions that cause them.

• Part 4, “PowerPC Instruction Set,” on page 41 provides detailed information on the

instruction field summary—including syntax and notation conventions. Also

included, is the entire PowerPC instruction set, sorted by mnemonic and opcode.

In this document, the term “60x” is used to denote a 32-bit microprocessor from the

PowerPC architecture family. 60x processors implement the PowerPC architecture as it is

specified for 32-bit addressing, which provides 32-bit effective (logical) addresses, integer

data types of 8, 16, and 32 bits, and floating-point data types of 32 and 64 bits (single-

precision and double-precision).

Table 1 contains acronyms and abbreviations that are used in this document. Note that the

meanings for some acronyms (such as SDR1 and XER) are historical, and the words for

which an acronym stands may not be intuitively obvious.

This document was created with FrameMaker 4.0.4

2

PowerPC Microprocessor Family: The Programmer’s Reference Guide

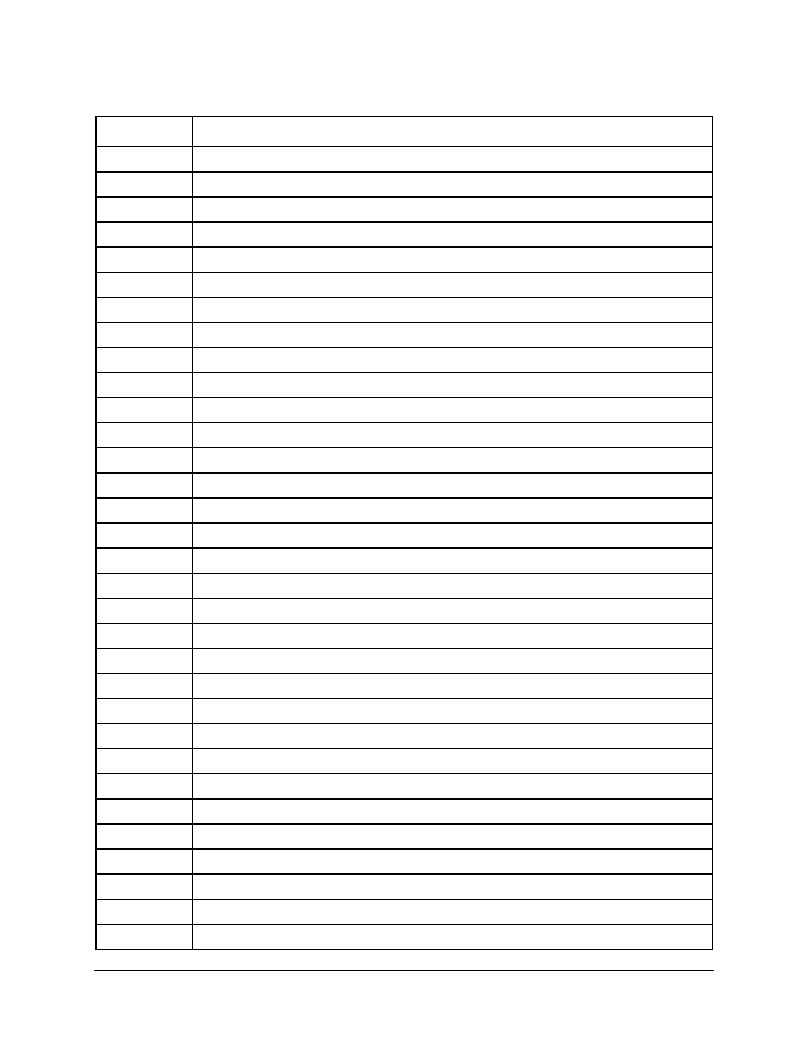

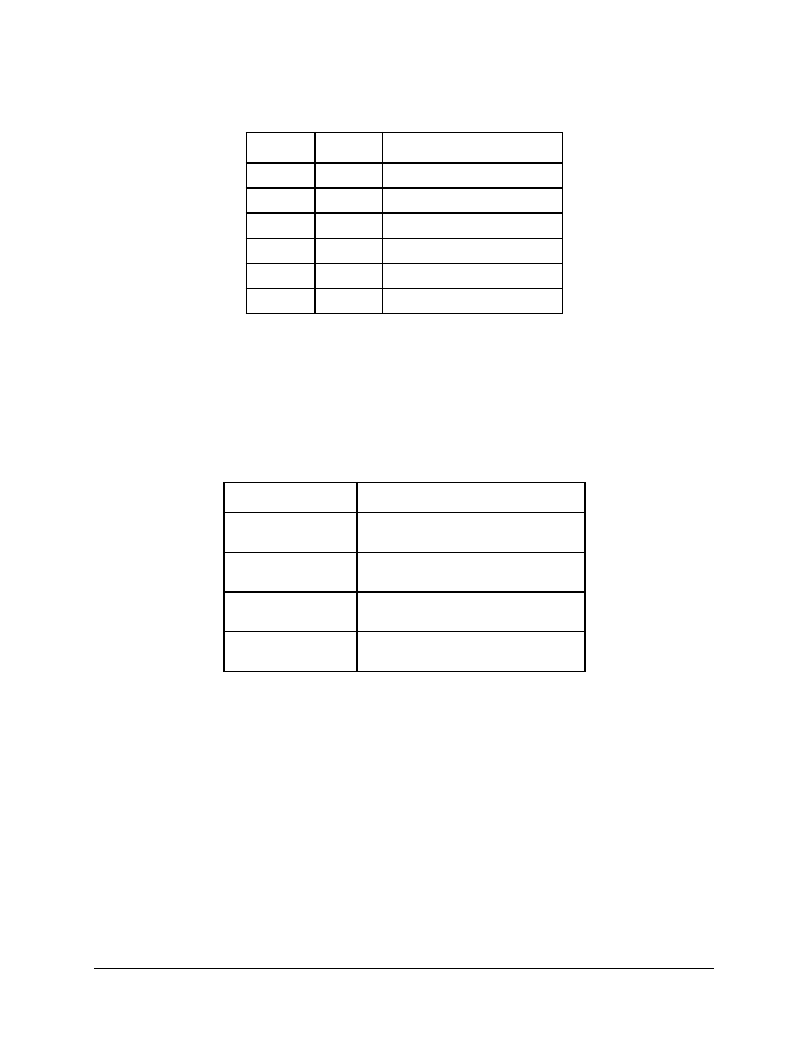

Table 1. Acronyms and Abbreviated Terms

Term Meaning

ASR Address space register

BAT Block address translation

BUID Bus unit ID

CR Condition register

CTR Count register

DAR Data address register

DBAT Data BAT

DEC Decrementer register

DSISR Register used for determining the source of a DSI exception

DTLB Data translation lookaside buffer

EA Effective address

EAR External access register

FPR Floating-point register

FPSCR Floating-point status and control register

GPR General-purpose register

IBAT Instruction BAT

IEEE Institute of Electrical and Electronics Engineers

IU Integer unit

LR Link register

MMU Memory management unit

msb Most significant bit

MSR Machine state register

NaN Not a number

No-Op No operation

OEA Operating environment architecture

PTE Page table entry

PTEG Page table entry group

PVR Processor version register

RISC Reduced instruction set computing

SDR1 Register that specifies the page table base address for virtual-to-physical address translation

SIMM Signed immediate value

SLB Segment lookaside buffer

PowerPC Microprocessor Family: The Programmer’s Reference Guide

3

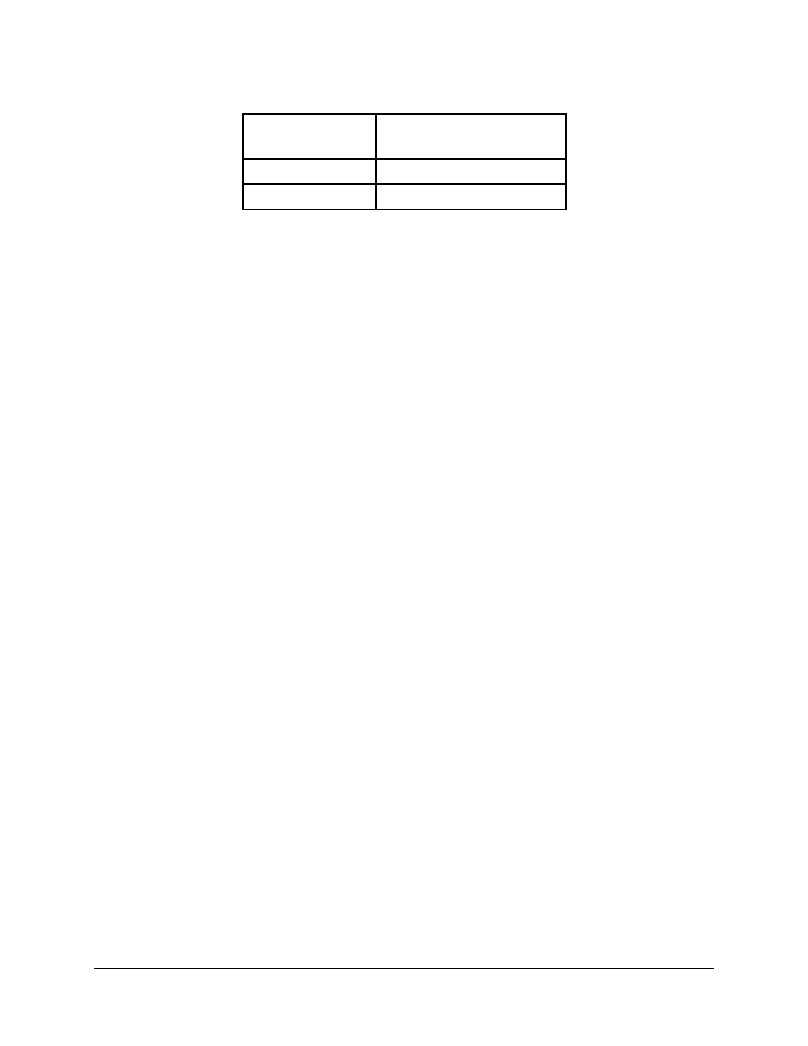

Table 2 describes instruction field notation conventions used in this document.

SPR Special-purpose register

SPRG

n

Registers available for general purposes

SR Segment register

SRR0 Machine status save/restore register 0

SRR1 Machine status save/restore register 1

TB Time base register

TLB Translation lookaside buffer

UIMM Unsigned immediate value

UISA User instruction set architecture

VEA Virtual environment architecture

XER Register used for indicating conditions such as carries and overflows for integer operations

Table 2. Instruction Field Conventions

The Architecture Specification Equivalent to:

BA, BB, BT

crb

A,

crb

B,

crb

D (respectively)

BF, BFA

crf

D,

crf

S (respectively)

Dd

DS ds

FLM FM

FRA, FRB, FRC, FRT, FRS

fr

A,

fr

B,

fr

C,

fr

D,

fr

S (respectively)

FXM CRM

RA, RB, RT, RS

r

A,

r

B,

r

D,

r

S (respectively)

SI SIMM

U IMM

UI UIMM

/, //, /// 0...0 (shaded)

Table 1. Acronyms and Abbreviated Terms (Continued)

Term Meaning

4

PowerPC Microprocessor Family: The Programmer’s Reference Guide

Part 1 Register Summary

This section describes the register organization defined by the three levels of the PowerPC

architecture—user instruction set architecture (UISA), virtual environment architecture

(VEA), and operating environment architecture (OEA). The PowerPC architecture defines

register-to-register operations for all computational instructions. Source data for these

instructions are accessed from the on-chip registers or are provided as immediate values

embedded in the opcode. The three-register instruction format allows specification of a

target register distinct from the two source registers, thus preserving the original data for

use by other instructions and reducing the number of instructions required for certain

operations. Data is transferred between memory and registers with explicit load and store

instructions only.

Figure 1 shows a graphic representation of the entire PowerPC register set. The number to

the right of the register name indicates the number that is used in the syntax of the

instruction operands to access the register (for example, the number used to access the XER

is SPR1).

Many of the SPRs can be accessed only by supervisor-level instructions; any attempt to

access these SPRs with user-level instructions results in a supervisor-level exception. Some

SPRs are implementation-specific. In some cases, not all of a register’s bits are

implemented in hardware. When a PowerPC microprocessor detects SPR encodings other

than those defined in this document, it either takes a program exception (if bit 0 of the SPR

encoding is set) or it treats the instruction as a no-op (if bit 0 of the SPR encoding is clear).

Note that the general purpose registers (GPRs), link register (LR), count register (CTR),

machine state register (MSR), data address register (DAR), SDR1, save and restore

registers 0 and 1 (SRR0 and SRR1), SPRG0–SPRG3, and data address breakpoint register

(DABR) are 64 bits in length in 64-bit implementations and 32 bits in length in 32-bit

implementations.

PowerPC Microprocessor Family: The Programmer’s Reference Guide

5

Figure 1. PowerPC Programming Model—Registers

FPR0

FPR1

FPR31

TBR 268

Time Base Facility

(Read-Only)

TBL

TBR 269

TBU

SUPERVISOR MODEL

Machine State Register

MSR

Processor Version Register

SPR 287PVR

Segment Registers

1

SR0

SR1

SR15

DSISR Register

SPR 18DSISR

Data Address Register

SPR 19DAR

Save and Restore Registers

SPR 26SRR0

SPR 27SRR1

SPRG Registers

SPR 272SPRG0

SPR 273SPRG1

SPR 274SPRG2

SPR 275SPRG3

SPR 22

Decrementer

DEC

Time Base Facility

(Write-Only)

SPR 284TBL

SPR 285TBU

SPR 282

External Address Register

3

EAR

SDR1 Register

SPR 25SDR1

Address Space Register

2

SPR 280ASR

Instruction BAT Registers

SPR 528IBAT0U

SPR 529IBAT0L

SPR 530IBAT1U

SPR 531IBAT1L

SPR 532IBAT2U

SPR 533IBAT2L

SPR 534IBAT3U

SPR 535IBAT3L

Data BAT Registers

SPR 536DBAT0U

SPR 537DBAT0L

SPR 538DBAT1U

SPR 539DBAT1L

SPR 540DBAT2U

SPR 541DBAT2L

SPR 542DBAT3U

SPR 543DBAT3L

Configuration Registers

Memory Management Registers

Exception Handling Registers

Miscellaneous Registers

SPR 1013DABR

Data Address

Breakpoint Register

3

1

These registers are in 32-bit implementations only.

2

These registers are in 64-bit implementations only.

3

These registers are optional in the PowerPC architecture.

SPR 1

USER MODEL

Floating-Point Status

and Control Register

CR

FPSCR

Condition Register

GPR0

GPR1

GPR31

General-Purpose Registers

Floating-Point Registers

XER

SPR 8

Link Register

LR

SPR 9

Count Register

CTR

XER Register

6

PowerPC Microprocessor Family: The Programmer’s Reference Guide

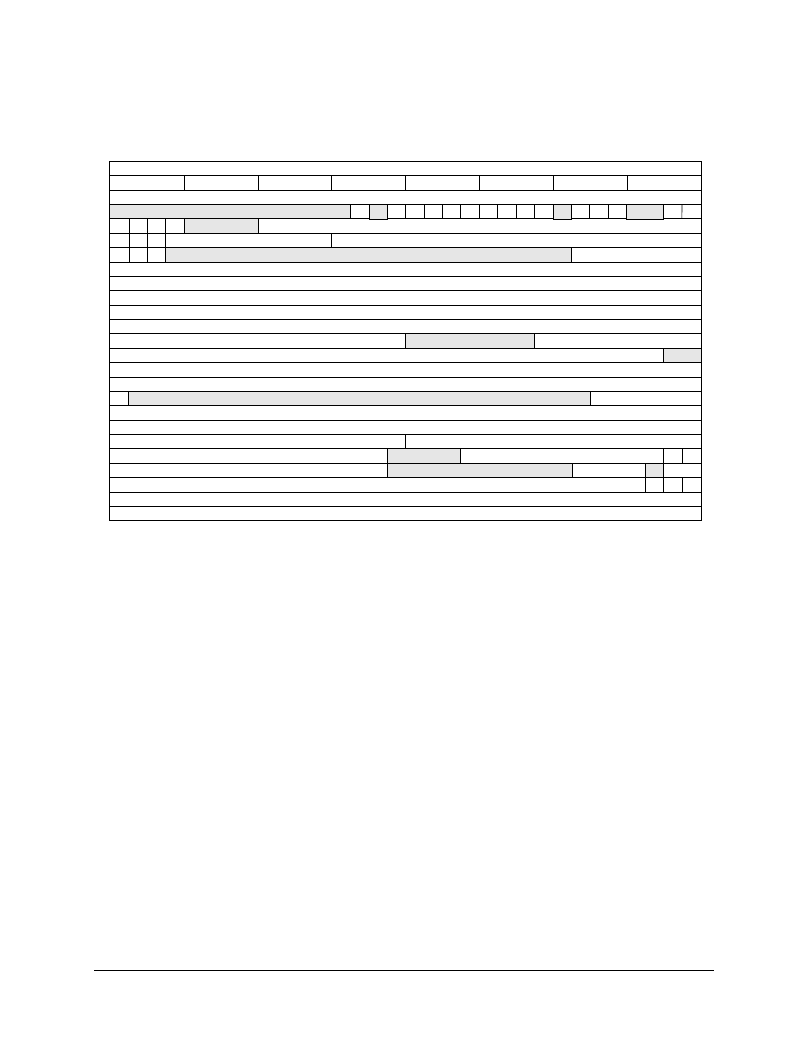

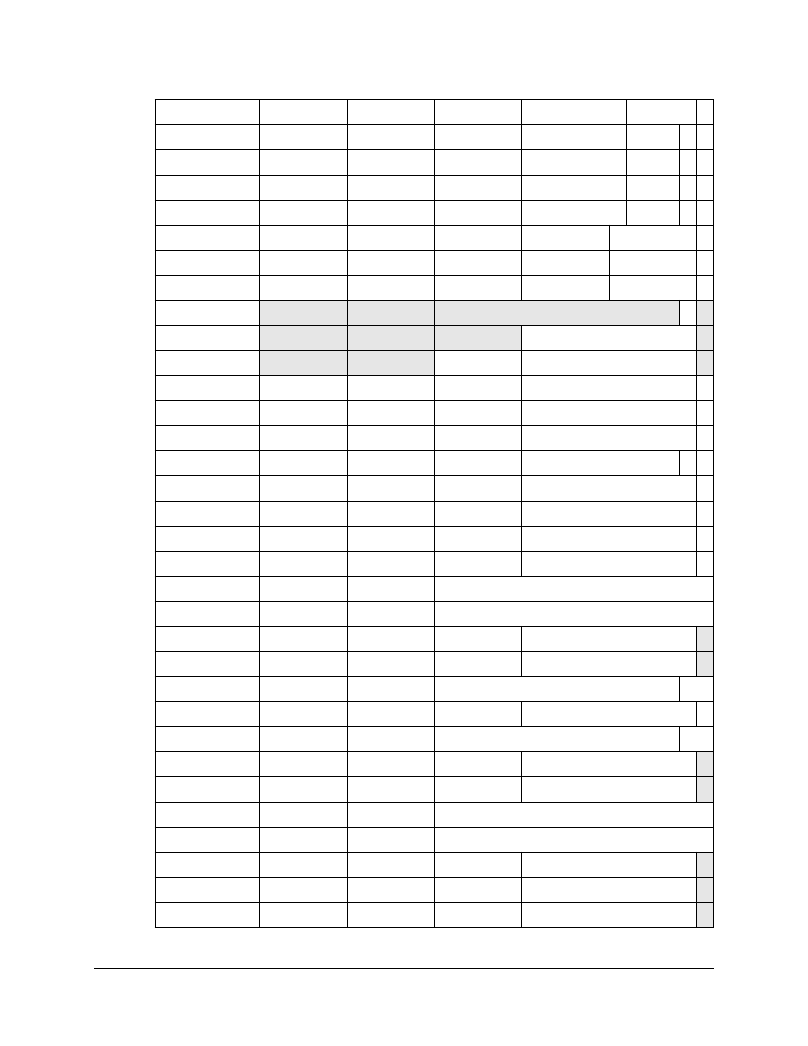

Table 3 provides a quick method by which to reference the SPR and TBR numbers and bit

fields for all 32-bit PowerPC registers. Note that reserved bits are shaded.

Table 3. Quick Reference Guide—32-Bit Registers

012345678910111213141516171819202122232425262728293031

Notes:

1. For all SPR numbers refer to Figure 1

2. Write-Only

3. Read-Only

012345678910111213141516

TBR 269

TBR 268

SPR 1013

SPR 529

SPR 528

SPR 287

SPR 285

SPR 284

SPR 282

SPR 272

SPR 27

SPR 26

SPR 25

Number

Number

GPR

n

Name

CR

MSR

LR

CTR

DAR

SDR1

SRR0

SRR1

SPRG

n

1

PVR

x

BAT

n

U

1

x

BAT

n

L

1

DABR

TB(L)

2

TBU

2

Name

0 0 0 0 0 0 0 0 0 0 0 0 0

POW

SPR 22

SPR 19

SPR 18

SPR 9

SPR 8

SPR 1

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

TB(L)

2

TBU

2

EAR

DEC

DSISR

XER

SR

n

[T=1]

SR

n

[T=0]

FPSCR

GPR

n

CR0 CR1 CR2 CR3 CR4 CR5 CR6 CR7

(For the FPSCR bits, refer to 1.4, “Floating-Point Status and Control Register (FPSCR),” on page 9.)

0

ILE PREE FP ME

FE0 FE1

BESE

0

IP IR DR

0 0

RI LE

VSID

0 0 0 0

TKs

Kp

N

T

Ks

Kp

BUID Controller-Specific Information

SO OV

CA

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Byte Count

Branch Address

CTR

DSISR

DAR

DEC

HTABORG

0 0 0 0 0 0 0

HTABMASK

SRR0

0 0

SRR1

SPRG

n

E

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

RID

TB(L)

TBU

TB(L)

TBU

Version Revision

BEPI

0 0 0 0

BL

Vs Vp

BRPN

0 0 0 0 0 0 0 0 0 0

WIMG

0

PP

DAB

BT

DW

DR

PowerPC Microprocessor Family: The Programmer’s Reference Guide

7

Number

0 1 2 3 4 5 6 7 8 9 101112131415161718192021222324252627282930313233343536373839404142434445464748495051525354555657585960616263

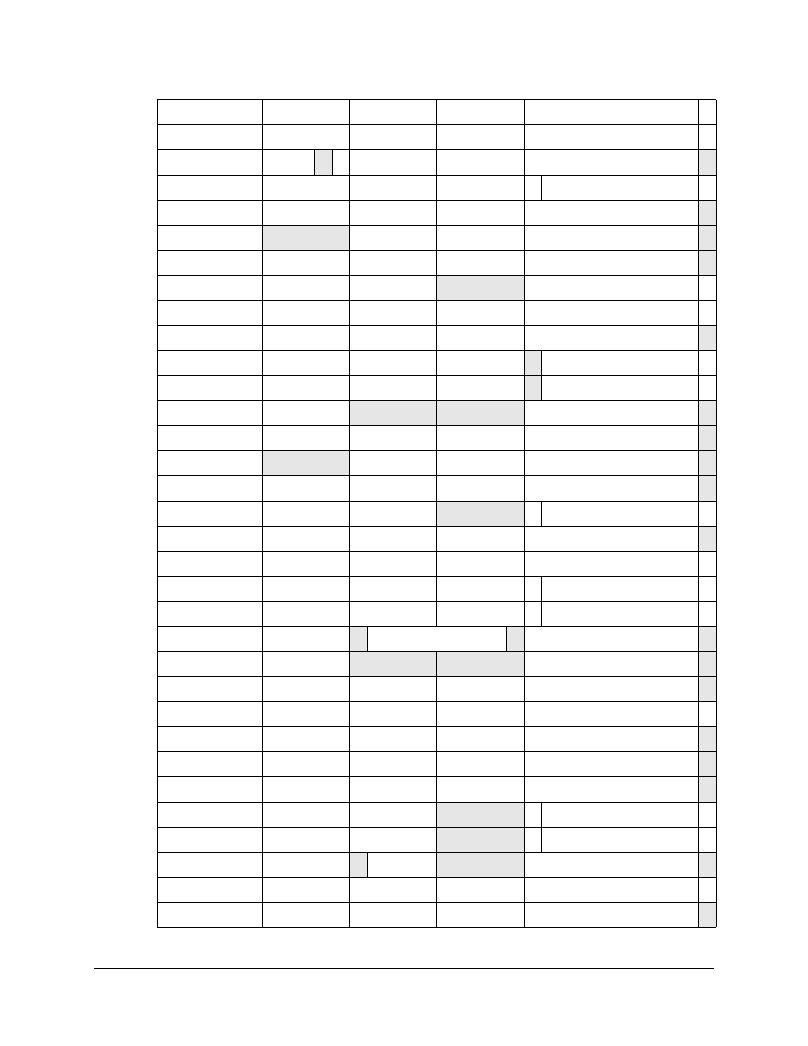

Table 4 provides a quick method by which to reference the SPR and TBR numbers and bit

fields for all 64-bit PowerPC registers. Note that reserved bits are shaded.

1.1 General-Purpose Registers (GPRs)

Integer data is manipulated in the processor’s 32 GPRs shown in Figure 2. These registers

are 64-bit registers in 64-bit implementations and 32-bit registers in 32-bit

implementations. The GPRs are accessed as source and destination registers in the

instruction syntax.

Figure 2. General-Purpose Registers (GPRs)

1.2 Floating-Point Registers (FPRs)

The PowerPC architecture provides thirty-two 64-bit FPRs as shown in Figure 3. These

registers are accessed as source and destination registers for floating-point instructions.

Each FPR supports the double-precision floating-point format. Every instruction that

interprets the contents of an FPR as a floating-point value uses the double-precision

floating-point format for this interpretation.

Table 4. Quick Reference Guide—64-Bit Registers

GPR0

GPR1

. . .

. . .

GPR31

0 63/31

TBR 269

TBR 268

SPR 1013

SPR 529

SPR 528

SPR 280

SPR 272

SPR 27

SPR 26

SPR 25

SPR 19

SPR 9

SPR 8

Number

GPR

n

Name

FPR

n

MSR

LR

CTR

DAR

SDR1

SRR0

SRR1

SPRG

n

1

ASR

x

BAT

n

U

1

x

BAT

n

L

1

DABR

TB(L)

2

TBU

2

Name

FPR

n

0

Branch Address

CTR

HTABORG

DAR

SRR0

SRR1

SPRG

n

BEPI

DAB

TB(L)

WIMG

TBU

0 0 0 0 0 0 0 0 0 0 0 0 0

HTABSIZE

0 0

Physical Address of Segment Table

0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0

BL

VsVp

BRPN

0 0 0 0 0 0 0 0 0 0

0

PP

B

T

D

W

D

R

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Notes:

1. For all SPR numbers refer to Figure 1

2. Read-only

For the MSR bits, refer to 1.8, “Machine State Register (MSR),” on page 16.)

0 1 2 3 4 5 6 7 8 9 101112131415161718192021222324252627282930313233343536373839404142434445464748495051525354555657585960616263

8

PowerPC Microprocessor Family: The Programmer’s Reference Guide

All floating-point arithmetic instructions operate on data located in FPRs and, with the

exception of compare instructions, place the result into an FPR. Information about the

status of floating-point operations is placed into the FPSCR and in some cases, into the CR

after the completion of instruction execution.

The floating-point arithmetic instructions produce intermediate results that may be

regarded as infinitely precise. After normalization or denormalization, if the precision of

the intermediate result cannot be represented in the destination format (single or double

precision), it is rounded to the specified precision before being placed in the target FPR.

The final result is then placed into the FPR in the double-precision format.

Figure 3. Floating-Point Registers (FPRs)

1.3 XER Register (XER)

The XER register (XER) is shown in Figure 4.

Figure 4. XER Register

Table 5 provides bit setting information for XER.

Table 5. XER Bit Definitions

Bit(s) Name Description

0 SO Summary overflow. The summary overflow bit (SO) is set whenever an instruction (except

mtspr

)

sets the overflow bit (OV). Once set, the SO bit remains set until it is cleared by an

mtspr

instruction (specifying the XER) or an

mcrxr

instruction. It is not altered by compare instructions,

nor by other instructions (except

mtspr

to the XER, and

mcrxr

) that cannot overflow. Executing

an

mtspr

instruction to the XER, supplying the values zero for SO and one for OV, causes SO to

be cleared and OV to be set.

1 OV Overflow. The overflow bit (OV) is set to indicate that an overflow has occurred during execution

of an instruction. Add, subtract from, and negate instructions having OE = 1 set the OV bit if the

carry out of the msb is not equal to the carry out of the msb + 1, and clear it otherwise. Multiply

low and divide instructions having OE = 1 set the OV bit if the result cannot be represented in 64

bits (

mulld

,

divd

,

divdu

) or in 32 bits (

mullw

,

divw

,

divwu

), and clear it otherwise. The OV bit is

not altered by compare instructions that cannot overflow (except

mtspr

to the XER, and

mcrxr

).

0 63

FPR0

FPR1

. . .

. . .

FPR31

SOOV CA 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Byte count

0 1 2 3 24 25 31

Reserved

PowerPC Microprocessor Family: The Programmer’s Reference Guide

9

1.4 Floating-Point Status and Control Register

(FPSCR)

Figure 5 shows the format of the floating-point status and control register (FPSCR).

Figure 5. Floating-Point Status and Control Register (FPSCR)

The FPSCR contains bits to do the following:

• Record exceptions generated by floating-point operations

• Record the type of the result produced by a floating-point operation

• Control the rounding mode used by floating-point operations

• Enable or disable the reporting of exceptions (invoking the exception handler)

Bits 0–23 are status bits. Bits 24–31 are control bits. Status bits in the FPSCR are updated

at the completion of the instruction execution.

Except for the floating-point enabled exception summary (FEX) and floating-point invalid

operation exception summary (VX), the exception condition bits in the FPSCR (bits 0–12

and 21–23) are sticky. Once set, sticky bits remain set until they are cleared by an

mcrfs

,

mtfsfi

,

mtfsf

, or

mtfsb0

instruction.

FEX and VX are the logical ORs of other FPSCR bits. Therefore, these two bits are not

listed among the FPSCR bits directly affected by the various instructions.

2 CA Carry. The carry bit (CA) is set during execution of the following instructions:

• Add carrying, subtract from carrying, add extended, and subtract from extended instructions

set CA if there is a carry out of the msb, and clear it otherwise.

• Shift right algebraic instructions set CA if any 1 bits have been shifted out of a negative

operand, and clear it otherwise.

The CA bit is not altered by compare instructions, nor by other instructions that cannot carry

(except shift right algebraic,

mtspr

to the XER, and

mcrxr

).

3–24 — Reserved

25–31 Byte

Count

This field specifies the number of bytes to be transferred by a Load String Word Indexed (

lswx

) or

Store String Word Indexed (

stswx

) instruction.

Table 5. XER Bit Definitions (Continued)

Bit(s) Name Description

0 1 2 3 4 5 6 7 8 9 101112131415 192021222324252627282930 31

VXIDI

VXISI

VXSNAN

VXZDZ

VXIMZ

VXVC

VXSOFT

VXSQRT

VXCVI

Reserved

FX FEXVX OX UX ZX XX FR FI FPRF 0 VE OE UE ZE XE NI RN

10

PowerPC Microprocessor Family: The Programmer’s Reference Guide

FPSCR bit settings are shown in Table 6.

Table 6. FPSCR Bit Settings

Bit(s) Name Description

0 FX Floating-point exception summary. Every floating-point instruction, except

mtfsfi

and

mtfsf

,

implicitly sets FPSCR[FX] if that instruction causes any of the floating-point exception bits in

the FPSCR to transition from 0 to 1. The

mcrfs

,

mtfsfi

,

mtfsf

,

mtfsb0

, and

mtfsb1

instructions can alter FPSCR[FX] explicitly. This is a sticky bit.

1 FEX Floating-point enabled exception summary. This bit signals the occurrence of any of the

enabled exception conditions. It is the logical OR of all the floating-point exception bits

masked by their respective enable bits. The

mcrfs

,

mtfsf

,

mtfsfi

,

mtfsb0

, and

mtfsb1

instructions cannot alter FPSCR[FEX] explicitly. This is not a sticky bit.

2 VX Floating-point invalid operation exception summary. This bit signals the occurrence of any

invalid operation exception. It is the logical OR of all of the invalid operation exceptions. The

mcrfs

,

mtfsf

,

mtfsfi

,

mtfsb0

, and

mtfsb1

instructions cannot alter FPSCR[VX] explicitly. This

is not a sticky bit.

3 OX Floating-point overflow exception. This is a sticky bit.

4 UX Floating-point underflow exception. This is a sticky bit.

5 ZX Floating-point zero divide exception. This is a sticky bit.

6 XX Floating-point inexact exception. This is a sticky bit.

FPSCR[XX] is the sticky version of FPSCR[FI]. The following rules describe how FPSCR[XX]

is set by a given instruction:

• If the instruction affects FPSCR[FI], the new value of FPSCR[XX] is obtained by logically

ORing the old value of FPSCR[XX] with the new value of FPSCR[FI].

• If the instruction does not affect FPSCR[FI], the value of FPSCR[XX] is unchanged.

7 VXSNAN Floating-point invalid operation exception for SNaN. This is a sticky bit.

8 VXISI Floating-point invalid operation exception for

∞

–

∞

. This is a sticky bit.

9 VXIDI Floating-point invalid operation exception for ∞ ÷ ∞. This is a sticky bit.

10 VXZDZ Floating-point invalid operation exception for 0 ÷ 0. This is a sticky bit.

11 VXIMZ Floating-point invalid operation exception for ∞ * 0. This is a sticky bit.

12 VXVC Floating-point invalid operation exception for invalid compare. This is a sticky bit.

13 FR Floating-point fraction rounded. The last arithmetic or rounding and conversion instruction that

rounded the intermediate result incremented the fraction. This bit is not sticky.

14 FI Floating-point fraction inexact. The last arithmetic or rounding and conversion instruction

either rounded the intermediate result (producing an inexact fraction) or caused a disabled

overflow exception. This is not a sticky bit. For more information regarding the relationship

between FPSCR[FI] and FPSCR[XX], see the description of the FPSCR[XX] bit.

PowerPC Microprocessor Family: The Programmer’s Reference Guide 11

Table 7 illustrates the floating-point result flags used by PowerPC processors. The result

flags correspond to FPSCR bits 15–19.

15–19 FPRF Floating-point result flags. For arithmetic, rounding, and conversion instructions the field is

based on the result placed into the target register, except that if any portion of the result is

undefined, the value placed here is undefined.

15 Floating-point result class descriptor (C). Arithmetic, rounding and conversion

instructions may set this bit with the FPCC bits to indicate the class of the result;

see Table 7.

16–19 Floating-point condition code (FPCC). Floating-point compare instructions always

set one of the FPCC bits to one and the other three FPCC bits to zero. Arithmetic,

rounding and conversion instructions may set the FPCC bits with the C bit to

indicate the class of the result. Note that in this case the high-order three bits of the

FPCC retain their relational significance indicating that the value is less than,

greater than, or equal to zero.

16 Floating-point less than or negative (FL or <)

17 Floating-point greater than or positive (FG or >)

18 Floating-point equal or zero (FE or =)

19 Floating-point unordered or NaN (FU or ?)

These are not sticky bits.

20 — Reserved

21 VXSOFT Floating-point invalid operation exception for software request. This is a sticky bit. This bit can

be altered only by the mcrfs, mtfsfi, mtfsf, mtfsb0, or mtfsb1 instructions.

22 VXSQRT Floating-point invalid operation exception for invalid square root. This is a sticky bit.

23 VXCVI Floating-point invalid operation exception for invalid integer convert. This is a sticky bit.

24 VE Floating-point invalid operation exception enable. This is not a sticky bit.

25 OE IEEE floating-point overflow exception enable. This is not a sticky bit.

26 UE IEEE floating-point underflow exception enable. This is not a sticky bit.

27 ZE IEEE floating-point zero divide exception enable. This is not a sticky bit.

28 XE Floating-point inexact exception enable. This is not a sticky bit.

29 NI Floating-point non-IEEE mode. If this bit is set, results need not conform with IEEE standards

and the other FPSCR bits may have meanings other than those described here. If the bit is set

and if all implementation-specific requirements are met and if an IEEE-conforming result of a

floating-point operation would be a denormalized number, the result produced is zero

(retaining the sign of the denormalized number). Any other effects associated with setting this

bit are described in the user’s manual for the implementation.

Effects of the setting of this bit is implementation-dependent. This is not a sticky bit.

30–31 RN Floating-point rounding control.

00 Round to nearest

01 Round toward zero

10 Round toward +infinity

11 Round toward –infinity

These are not sticky bits.

Table 6. FPSCR Bit Settings (Continued)

Bit(s) Name Description

12 PowerPC Microprocessor Family: The Programmer’s Reference Guide

1.5 Condition Register (CR)

The format of the condition register (CR) is shown in Figure 6.

Figure 6. Condition Register (CR)

The CR fields can be set in one of the following ways:

• Specified fields of the CR can be set by a move instruction (mtcrf) to the CR from

a GPR.

• A specified field of the CR can be moved to another CR field with the mcrf

instruction.

• A specified field of the XER can be copied to the CR by the mcrxr instruction.

• A specified field of the FPSCR can be copied to the CR by the mcrfs instruction.

• Condition register logical instructions can be used to perform logical operations on

specified bits in the condition register.

• CR0 can be the implicit result of an integer instruction.

• CR1 can be the implicit result of a floating-point instruction.

• A specified CR field can indicate the result of either an integer or floating-point

compare instruction.

Note that branch instructions are provided to test individual CR bits.

Table 7. Floating-Point Result Flags in FPSCR

Result Flags (Bits 15–19)

Result Value Class

C<>=?

10001Quiet NaN

01001–Infinity

01000–Normalized number

11000–Denormalized number

10010–Zero

00010+Zero

10100+Denormalized number

00100+Normalized number

00101+Infinity

CR0 CR1 CR2 CR3 CR4 CR5 CR6 CR7

0 3 4 7 8 1112 1516 19 20 2324 2728 31

PowerPC Microprocessor Family: The Programmer’s Reference Guide 13

The following tables, Table 8–Table 10, provide bit setting information for CR0, CR1, and

the CRn fields, respectively.

Table 8. Bit Settings for CR0 Field of CR

CR0

Bit

Description

0 Negative (LT)—This bit is set when the result is negative.

1 Positive (GT)—This bit is set when the result is positive (and not zero).

2 Zero (EQ)—This bit is set when the result is zero.

3 Summary overflow (SO)—This is a copy of the final state of XER[SO] at

the completion of the instruction.

Table 9. Bit Settings for CR1 Field of CR

CR1

Bit

Description

4 Floating-point exception (FX)—This is a copy of the final state of

FPSCR[FX] at the completion of the instruction.

5 Floating-point enabled exception (FEX)—This is a copy of the final

state of FPSCR[FEX] at the completion of the instruction.

6 Floating-point invalid exception (VX)—This is a copy of the final state

of FPSCR[VX] at the completion of the instruction.

7 Floating-point overflow exception (OX)—This is a copy of the final

state of FPSCR[OX] at the completion of the instruction.

Note: For more information on the FPSCR refer to Section 1.4, “Floating-Point

Status and Control Register (FPSCR).”

14 PowerPC Microprocessor Family: The Programmer’s Reference Guide

1.6 Link Register (LR)

The link register (LR) is a 64-bit register in 64-bit implementations and a 32-bit register in

32-bit implementations. The LR supplies the branch target address for the Branch

Conditional to Link Register (bclrx) instruction, and can be used to hold the logical address

of the instruction that follows a branch and link instruction. The format of LR is shown in

Figure 7.

Figure 7. Link Register (LR)

Note that although the two least-significant bits can accept any values written to them, they

are ignored when the LR is used as an address. The link register can be accessed by the

mtspr and mfspr instructions using SPR8. Fetching instructions along the target path

(loaded by an mtspr instruction) is possible provided the link register is loaded sufficiently

ahead of the branch instruction. It is possible for a PowerPC microprocessor to fetch along

a target path loaded by a branch and link instruction.

Both conditional and unconditional branch instructions include the option of placing the

effective address of the instruction following the branch instruction in the LR.

Table 10. CR

n

Field Bit Settings for Compare Instructions

CR

n

Bit

1

Description

2

0 Less than or floating-point less than (LT, FL).

For integer compare instructions: rA < SIMM or rB (signed comparison) or

rA < UIMM or rB (unsigned comparison).

For floating-point compare instructions: frA < frB.

1 Greater than or floating-point greater than (GT, FG).

For integer compare instructions: rA > SIMM or rB (signed comparison) or

rA > UIMM or rB (unsigned comparison).

For floating-point compare instructions: frA > frB.

2 Equal or floating-point equal (EQ, FE).

For integer compare instructions: rA = SIMM, UIMM, or rB.

For floating-point compare instructions: frA = frB.

3 Summary overflow or floating-point unordered (SO, FU).

For integer compare instructions: This is a copy of the final state of XER[SO]

at the completion of the instruction.

For floating-point compare instructions: One or both of frA and frB is a Not a

Number (NaN).

Notes:

1. Here, the bit indicates the bit number in any one of the four-bit subfields, CR0–CR7.

2. For a complete description of instruction syntax conventions, refer to Table 31.

Branch Address

0 63/31

PowerPC Microprocessor Family: The Programmer’s Reference Guide 15

1.7 Count Register (CTR)

The count register (CTR) is a 64-bit register in 64-bit implementations and a 32-bit register

in 32-bit implementations. The CTR can hold a loop count that can be decremented during

execution of branch instructions that contain an appropriately coded BO field. If the value

in CTR is 0 before being decremented, it is –1 afterward. The CTR can also provide the

branch target address for the Branch Conditional to Count Register (bcctrx) instruction.

The CTR is shown in Figure 8.

Figure 8. Count Register (CTR)

Fetching instructions along the target path is also possible provided the count register is

loaded sufficiently ahead of the branch instruction.

The count register can be accessed by the mtspr and mfspr instructions by specifying

SPR9. In branch conditional instructions, the BO field specifies the conditions under which

the branch is taken. The first four bits of the BO field specify how the branch is affected by

or affects the CR and the CTR. The encoding for the BO field is shown in Table 11.

Table 11. BO Operand Encodings

BO Description

0000

y

Decrement the CTR, then branch if the decremented CTR ≠ 0 and the condition is FALSE.

0001

y

Decrement the CTR, then branch if the decremented CTR = 0 and the condition is FALSE.

001

zy

Branch if the condition is FALSE.

0100

y

Decrement the CTR, then branch if the decremented CTR ≠ 0 and the condition is TRUE.

0101

y

Decrement the CTR, then branch if the decremented CTR = 0 and the condition is TRUE.

011

zy

Branch if the condition is TRUE.

1

z

00

y

Decrement the CTR, then branch if the decremented CTR ≠ 0.

1

z

01

y

Decrement the CTR, then branch if the decremented CTR = 0.

1

z

1

zz

Branch always.

The

z

indicates a bit that is ignored. The

z

bits should be cleared to zero, as they may be assigned a

meaning in some future version of the PowerPC architecture.

The

y

bit provides a hint about whether a conditional branch is likely to be taken and is used by some

PowerPC implementations to improve performance. Other implementations may ignore the

y

bit.

CTR

0 63/31

16 PowerPC Microprocessor Family: The Programmer’s Reference Guide

1.8 Machine State Register (MSR)

The machine state register (MSR), is a 64-bit register on 64-bit implementations (see

Figure 9) and a 32-bit register in 32-bit implementations (see Figure 10).

Figure 9. Machine State Register (MSR)—64-bit Implementations

Figure 10. Machine State Register (MSR)—32-bit Implementations

Table 12 shows the bit definitions for the MSR. Full function reserved bits are saved in

SRR1 when an exception occurs; partial function reserved bits are not saved.

Table 12. MSR Bit Settings

Bit(s)

Name Description

64 Bit 32 Bit

0 — SF Sixty-four bit mode

0 The 64-bit processor runs in 32-bit mode.

1 The 64-bit processor runs in 64-bit mode. Note that this is the default setting.

1–32 0 — Reserved. Full function.

33–36 1–4 — Reserved. Partial function.

37–41 5–9 — Reserved. Full function.

42–44 10–12 — Reserved. Partial function.

45 13 POW Power management enable

0 Power management disabled (normal operation mode).

1 Power management enabled (reduced power mode).

Note: Power management functions are implementation-dependent. If the function

is not implemented, this bit is treated as reserved.

46 14 — Reserved—Implementation-specific

47 15 ILE Exception little-endian mode. When an exception occurs, this bit is copied into

MSR[LE] to select the endian mode for the context established by the exception.

48 16 EE External interrupt enable

0 While the bit is cleared the processor delays recognition of external interrupts

and decrementer exception conditions.

1 The processor is enabled to take an external interrupt or the decrementer

exception.

0 1 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 6162 63

SF 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 POW 0 ILE EE PR FPMEFE0 SE BE FE1 0 IP IR DR 0 0 RI LE

Reserved

01213141516171819202122232425262728293031

0 0 0 0 0 0 0 0 0 0 0 0 0

POW 0 ILE EE PR FP MEFE0 SE BE FE1 0 IP IR DR 0 0 RI LE

Reserved

PowerPC Microprocessor Family: The Programmer’s Reference Guide 17

49 17 PR Privilege level

0 The processor can execute both user- and supervisor-level instructions.

1 The processor can only execute user-level instructions.

50 18 FP Floating-point available

0 The processor prevents dispatch of floating-point instructions, including

floating-point loads, stores, and moves.

1 The processor can execute floating-point instructions.

51 19 ME Machine check enable

0 Machine check exceptions are disabled.

1 Machine check exceptions are enabled.

52 20 FE0 Floating-point exception mode 0 (see Table 13).

53 21 SE Single-step trace enable (Optional)

0 The processor executes instructions normally.

1 The processor generates a single-step trace exception upon the successful

execution of the next instruction.

Note: If the function is not implemented, this bit is treated as reserved.

54 22 BE Branch trace enable (Optional)

0 The processor executes branch instructions normally.

1 The processor generates a branch trace exception after completing the

execution of a branch instruction, regardless of whether or not the branch was

taken.

Note: If the function is not implemented, this bit is treated as reserved.

55 23 FE1 Floating-point exception mode 1 (see Table 13).

56 24 — Reserved. Full function.

57 25 IP Exception prefix. The setting of this bit specifies whether an exception vector offset

is prepended with Fs or 0s. In the following description,

nnnnn

is the offset of the

exception. See Table 30.

0 Exceptions are vectored to the physical address 0x000

n_nnnn

in 32-bit

implementations and 0x0000_0000_000

n

_

nnnn

in 64-bit implementations.

1 Exceptions are vectored to the physical address 0xFFF

n_nnnn

in 32-bit

implementations and 0xFFFF_FFFF_FFF

n

_

nnnn

in 64-bit implementations.

58 26 IR Instruction address translation

0 Instruction address translation is disabled.

1 Instruction address translation is enabled.

59 27 DR Data address translation

0 Data address translation is disabled.

1 Data address translation is enabled.

60–61 28–29 — Reserved. Full function.

62 30 RI Recoverable exception (for system reset and machine check exceptions).

0 Exception is not recoverable.

1 Exception is recoverable.

63 31 LE Little-endian mode enable

0 The processor runs in big-endian mode.

1 The processor runs in little-endian mode.

Table 12. MSR Bit Settings (Continued)

Bit(s)

Name Description

64 Bit 32 Bit

18 PowerPC Microprocessor Family: The Programmer’s Reference Guide

The floating-point exception mode bits (FE0–FE1) are interpreted as shown in Table 13.

Note that these bits can be logically ORed, so that if either is set the processor operates in

precise mode.

Table 14 indicates the initial state of the MSR.

Table 13. Floating-Point Exception Mode Bits

FE0 FE1 Mode

0 0 Floating-point exceptions disabled

0 1 Floating-point imprecise nonrecoverable

1 0 Floating-point imprecise recoverable

1 1 Floating-point precise mode

Table 14. State of MSR at Power Up

Bit(s)

Name

64-Bit

Description

32-Bit

Description

64 Bit 32 Bit

0—SF1 —

1–44 0–12 — Unspecified

1

Unspecified

1

45 13 POW 0 0

46 14 — Unspecified

1

Unspecified

1

47 15 ILE 0 0

48 16 EE 0 0

49 17 PR 0 0

50 18 FP 0 0

51 19 ME 0 0

52 20 FE0 0 0

53 21 SE 0 0

54 22 BE 0 0

55 23 FE1 0 0

56 24 — Unspecified

1

Unspecified

1

57 25 IP 1

2

1

2

58 26 IR 0 0

59 27 DR 0 0

PowerPC Microprocessor Family: The Programmer’s Reference Guide 19

1.9 Processor Version Register (PVR)

The processor version register (PVR) is a 32-bit, read-only register that contains a value

identifying the specific version (model) and revision level of the PowerPC processor (see

Figure 11). The contents of the PVR can be copied to a GPR by the mfspr instruction. Read

access to the PVR is supervisor-level only; write access is not provided.

Figure 11. Processor Version Register (PVR)

The PVR consists of two 16-bit fields:

• Version (bits 0–15)—A 16-bit number that uniquely determines a particular

processor version and version of the PowerPC architecture. This number can be used

to determine the version of a processor; it may not distinguish between different

product models if more than one model uses the same processor.

• Revision (bits 16–31)—A 16-bit number that distinguishes between various releases

of a particular version (that is, an engineering change level). The value of the

revision portion of the PVR is implementation-specific. The processor revision level

is changed for each revision of the device.

60–61 28–29 — Unspecified

1

Unspecified

1

62 30 RI 0 0

63 31 LE 0 0

Notes:

1. Unspecified can be either 0 or 1

2. 1 is typical, but might be 0

Table 14. State of MSR at Power Up (Continued)

Bit(s)

Name

64-Bit

Description

32-Bit

Description

64 Bit 32 Bit

0151631

Version Revision

20 PowerPC Microprocessor Family: The Programmer’s Reference Guide

1.10 BAT Registers

Figure 12 and Figure 13 show the format of the upper and lower BAT registers for 64-bit

PowerPC processors.

Figure 12. Upper BAT Register—64-Bit Implementations

Figure 13. Lower BAT Register—64-Bit Implementations

Figure 14 and Figure 15 show the format of the upper and lower BAT registers for 32-bit

PowerPC processors.

Figure 14. Format of Upper BAT Registers—32-Bit Implementations

Figure 15. Format of Lower BAT Registers—32-Bit Implementations

046475051616263

BEPI 0 0 0 0 BL Vs Vp

Reserved

BRPN 0 0 0 0 0 0 0 0 0 0 WIMG 0 PP

0 4647 5657 60 6162 63

Reserved

BEPI 0 0 0 0 BL Vs Vp

014151819293031

Reserved

01415242528293031

BRPN 0 0 0 0 0 0 0 0 0 0 WIMG 0 PP

Reserved

PowerPC Microprocessor Family: The Programmer’s Reference Guide 21

Table 15 describes the bits in the BAT registers.

Table 16 lists the BAT area lengths encoded in the BL field of the upper BAT registers.

Table 15. BAT Registers—Field and Bit Descriptions

Upper/

Lower

BAT

Bits

Name Description

64 Bit 32 Bit

Upper

BAT

Register

0–46 0–14 BEPI Block effective page index. This field is compared with high-order bits

of the logical address to determine if there is a hit in that BAT array

entry. (The architecture specification refers to logical address as

effective address.)

46–50 15–18 — Reserved

51–61 19–29 BL Block length. BL is a mask that encodes the size of the block. Values

for this field are listed in Table 16.

62 30 Vs Supervisor mode valid bit. This bit interacts with MSR[PR] to

determine if there is a match with the logical address.

63 31 Vp User mode valid bit. This bit also interacts with MSR[PR] to

determine if there is a match with the logical address.

Lower

BAT

Register

0–46 0–14 BRPN This field is used in conjunction with the BL field to generate high-

order bits of the physical address of the block.

47–56 15–24 — Reserved

57–60 25–28 WIMG Memory/cache access mode bits

W Write-through

I Caching-inhibited

M Memory coherence

G Guarded

61 29 — Reserved

62–63 30–31 PP Protection bits for block

Table 16. BAT Area Lengths

BAT Area

Length

BL Encoding

128 Kbytes 000 0000 0000

256 Kbytes 000 0000 0001

512 Kbytes 000 0000 0011

1 Mbyte 000 0000 0111

2 Mbytes 000 0000 1111

4 Mbytes 000 0001 1111

8 Mbytes 000 0011 1111

16 Mbytes 000 0111 1111

32 Mbytes 000 1111 1111

22 PowerPC Microprocessor Family: The Programmer’s Reference Guide

1.11 SDR1

The SDR1 is a 64-bit register in 64-bit implementations and a 32-bit register in 32-bit

implementations. Refer to Section 2.3.3, “SDR1 Register Definitions,” for a complete

description of SDR1.

1.12 Address Space Register (ASR)

The address space register (ASR) is a 64-bit SPR that holds 0–51 of the segment table’s

physical address. The segment table is the segment descriptor mechanism for 64-bit

implementations. For more detailed information about the ASR, refer to Section 2.2.1.1,

“Address Space Register (ASR).”

1.13 Segment Registers (SRs)

Segment registers are used in page and direct-store segment address translations. Refer to

Section 2.2, “Segment Descriptor Definitions,” for information on segment registers.

1.14 Data Address Register (DAR)

The DAR is a 64-bit register in 64-bit implementations and a 32-bit register in 32-bit

implementations. The DAR is shown in Figure 16.

Figure 16. Data Address Register (DAR)

The effective address generated by a memory access instruction is placed in the DAR if the

access causes an exception (for example, an alignment exception). If the exception occurs

in a 64-bit implementation operating in 32-bit mode, the high-order 32 bits of the DAR are

cleared.

64 Mbytes 001 1111 1111

128 Mbytes 011 1111 1111

256 Mbytes 111 1111 1111

Table 16. BAT Area Lengths (Continued)

BAT Area

Length

BL Encoding

DAR

0 63

PowerPC Microprocessor Family: The Programmer’s Reference Guide 23

1.15 SPRG0–SPRG3

SPRG0–SPRG3 are 64-bit or 32-bit registers, depending on the type of PowerPC

microprocessor. They are provided for general operating system use, such as performing a

fast state save or for supporting multiprocessor implementations. The formats of SPRG0

through SPRG3 are shown in Figure 17.

Figure 17. SPRG0–SPRG3

Table 17 provides a description of conventional uses of SPRG0–SPRG3.

1.16 DSISR

The 32-bit DSISR, shown in Figure 18, identifies the cause of DSI and alignment

exceptions.

Figure 18. DSISR

1.17 Machine Status Save/Restore Register 0 (SRR0)

The SRR0 is a 64-bit register in 64-bit implementations and a 32-bit register in 32-bit

implementations. SRR0 is used to save machine status on exceptions and restore machine

Table 17. Conventional Uses of SPRG0–SPRG3

Register Description

SPRG0 Software may load a unique physical address in this register to identify an area of memory

reserved for use by the first-level exception handler. This area must be unique for each processor

in the system.

SPRG1 This register may be used as a scratch register by the first-level exception handler to save the

content of a GPR. That GPR then can be loaded from SPRG0 and used as a base register to

save other GPR’s to memory.

SPRG2 This register may be used by the operating system as needed.

SPRG3 This register may be used by the operating system as needed.

0 63

SPRG0

SPRG1

SPRG2

SPRG3

0 63

DSISR

0 31

24 PowerPC Microprocessor Family: The Programmer’s Reference Guide

status when an rfi instruction is executed. It also holds the EA for the instruction that

follows the System Call (sc) instruction. The format of SRR0 is shown in Figure 19. For

32-bit implementations, the format of SRR0 follows the low-order bits (32–63) of

Figure 19.

Figure 19. Machine Status Save/Restore Register 0 (SRR0)

When an exception occurs, SRR0 is set to point to an instruction such that all prior

instructions have completed execution and no subsequent instruction has begun execution.

When rfi is executed, the contents of SRR0 are copied to the next instruction address

(NIA)—the 64- or 32-bit address of the next instruction to be executed. The instruction

addressed by SRR0 may not have completed execution, depending on the exception type.

SRR0 addresses either the instruction causing the exception or the instruction that

immediately follows. The instruction addressed can be determined from the exception type

and status bits.

If the exception occurs in 32-bit mode of the 64-bit implementation, the high-order 32 bits

of SRR0 are cleared and the high-order 32 bits of the NIA are cleared when returning to

32-bit mode.

Note that in some implementations, every instruction fetch, when MSR[IR] = 1, and every

instruction execution requiring address translation when MSR[DR] = 1, may modify

SRR0.

1.18 Machine Status Save/Restore Register 1 (SRR1)

The SRR0 is a 64-bit register in 64-bit implementations and a 32-bit register in 32-bit

implementations. SRR1 is used to save machine status on exceptions and to restore

machine status when an rfi instruction is executed. The format of SRR1 is shown in

Figure 20.

Figure 20. Machine Status Save/Restore Register 1 (SRR1)

On 64-bit implementations, when an exception occurs, bits 33–36 and 42–47 of SRR1 are

loaded with exception-specific information and bits 0–32, 37–41, and 48–63 of MSR are

placed into the corresponding bit positions of SRR1.

SRR0

0 61 62 63

0 0

Reserved

SRR1

0 63

PowerPC Microprocessor Family: The Programmer’s Reference Guide 25

For 32-bit implementations, when an exception occurs, bits 1–4 and 10–15 of SRR1 are

loaded with exception-specific information and bits 0, 5–9, and 16–31 of MSR are placed

into the corresponding bit positions of SRR1.

Note that, in some implementations, every instruction fetch when MSR[IR] = 1, and every

instruction execution requiring address translation when MSR[DR] = 1, may modify

SRR1.

1.19 Time Base Facility (TB)

The time base (TB), shown in Figure 21, is a 64-bit structure that contains a 64-bit unsigned

integer that is incremented periodically. Each increment adds 1 to the low-order bit (bit 63).

The frequency at which the counter is incremented is implementation-dependent.

Figure 21. Time Base (TB)

The TB increments until its value becomes 0xFFFF_FFFF_FFFF_FFFF (2

64

– 1). At the

next increment its value becomes 0x0000_0000_0000_0000. Note that there is no explicit

indication that this has occurred (that is, no exception is generated).

The period of the time base depends on the driving frequency. The TB is implemented such

that the following requirements are satisfied:

1. Loading a GPR from the time base has no effect on the accuracy of the time

base.

2. Storing a GPR to the time base replaces the value in the time base with the value in

the GPR.

The PowerPC VEA does not specify a relationship between the frequency at which the time

base is updated and other frequencies, such as the processor clock. The TB update

frequency is not required to be constant; however, for the system software to maintain time

of day and operate interval timers, one of two things is required:

• The system provides an implementation-dependent exception to software whenever

the update frequency of the time base changes and a means to determine the current

update frequency; or

• The system software controls the update frequency of the time base.

Note that if the operating system initializes the TB to some ‘reasonable’ value and the

update frequency of the TB is constant, the TB can be used as a source of values that

increase at a constant rate, such as for time stamps in trace entries.

031031

TBU—Upper 32 bits of time base

TBL—Lower 32 bits of time base

26 PowerPC Microprocessor Family: The Programmer’s Reference Guide

Even if the update frequency is not constant, values read from the TB are monotonically

increasing (except when the TB wraps from 2

64

– 1 to 0). If a trace entry is recorded each

time the update frequency changes, the sequence of TB values can be post-processed to

become actual time values.

For information on reading, writing, and computing time of day on the time base, refer to

Chapter 2, “PowerPC Register Set,” The Programming Environments Manual.

1.20 Decrementer Register (DEC)

The DEC, shown in Figure 22, is a 32-bit decrementing counter that provides a mechanism

for causing a decrementer exception after a programmable delay. The DEC frequency is

based on the same implementation-dependent frequency that drives the time base.

Figure 22. Decrementer Register (DEC)

For information on writing and reading the DEC, refer to Chapter 2, “PowerPC Register

Set,” The Programming Environments Manual.

1.21 Data Address Breakpoint Register (DABR)

The data address breakpoint facility is controlled by the DABR, a 64-bit register in 64-bit

implementations and a 32-bit register in 32-bit implementations. The data address

breakpoint facility is optional to the PowerPC architecture, as is the DABR. However, if

the data address breakpoint facility is implemented, it is recommended, but not required,

that it be implemented as described in this section.

The data address breakpoint facility provides a means to detect accesses to a designated

double word. The address comparison is done on an effective address, and it applies to data

accesses only. It does not apply to instruction fetches.

The DABR is shown in Figure 23.

Figure 23. Data Address Breakpoint Register—64-Bit Implementations

DEC

0 31

0 60 61 62 63

DAB BT DW DR

PowerPC Microprocessor Family: The Programmer’s Reference Guide 27

Table 18 describes the fields in the DABR.

A data address breakpoint match is detected for a load or store instruction if the three

following conditions are met for any byte accessed:

• EA[0–60] = DABR[DAB]

• MSR[DR] = DABR[BT]

• The instruction is a store and DABR[DW] = 1, or the instruction is a load and

DABR[DR] = 1.

In 32-bit mode of a 64-bit implementation, the high-order 32 bits of the EA are treated as

zero for the purpose of detecting a match.

1.22 External Access Register (EAR)

The EAR is an optional 32-bit SPR that controls access to the external control facility and

identifies the target device for external control operations. The external control facility

provides a means for user-level instructions to communicate with special external devices.

The EAR is shown in Figure 24. Note that the EAR is an optional register.

Figure 24. External Access Register (EAR)

The high-order bits of the resource ID (RID) field that correspond to bits of the RID beyond

the width of the RID supported by a particular implementation are treated as reserved bits.

The EAR register is provided to support the External Control In Word Indexed (eciwx) and

External Control Out Word Indexed (ecowx) instructions. Access to the EAR is supervisor-

level, thus the operating system can determine which tasks are allowed to issue external

access instructions and when they are allowed to do so. The bit settings for the EAR are

described in Table 19.

Table 18. DABR—Field Descriptions

Bits

Name Description

64 Bit 32 Bit

0–60 0–28 DAB Data address breakpoint

61 29 BT Breakpoint translation enable

62 30 DW Data write enable

63 31 DR Data read enable

01 25 26 31

E 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 RID

Reserved

28 PowerPC Microprocessor Family: The Programmer’s Reference Guide

The data access of eciwx and ecowx is performed as though the memory access mode bits

(WIMG) were 0101. For example, if the external control facility is used to support a

graphics adapter, the ecowx instruction could be used to send the translated physical

address of a buffer containing graphics data to the graphics device. The eciwx instruction

could be used to load status information from the graphics adapter.

This register can also be accessed by using the mtspr and mfspr instructions.

Part 2 Memory Control Model

Memory in the PowerPC OEA is divided into 256-Mbyte segments. This segmented

memory model provides a way to map 4-Kbyte pages of effective addresses to 4-Kbyte

pages in physical memory (page address translation), while providing the programming

flexibility afforded by a large virtual address space (80 or 52 bits).

The page address translation uses segment descriptors, which provide virtual address and

protection information, and page table entries (PTEs), which provide the physical address

and page protection information. The segment descriptors are programmed by the

operating system to provide the virtual ID for a segment. In addition, the operating system

also creates the page tables in memory that provide the virtual to physical address mappings

(in the form of PTEs) for the pages in memory.

Segments in the OEA are defined as one of the following two types:

• Memory segment—An effective address in these segments represents a virtual

address that is used to define the physical address of the page.

• Direct-store segment—References made to direct-store segments do not use the

virtual paging mechanism of the processor.

The T bit in the segment descriptor selects between memory segments and direct-store

segments, as shown in Table 20.

Table 19. External Access Register (EAR) Bit Settings

Bit Name Description

0 E Enable bit

1 Enabled

0 Disabled

If this bit is set, the eciwx and ecowx instructions can perform the

specified external operation. If the bit is cleared, an eciwx or ecowx

instruction causes a DSI exception.

1–25 — Reserved

26–31 RID Resource ID

PowerPC Microprocessor Family: The Programmer’s Reference Guide 29

All accesses generated by the processor map to a segment descriptor. If MSR[IR] = 0 or

MSR[DR] = 0 for an instruction or data access, respectively, then real addressing mode

translation is performed. Otherwise, if T = 0 in the corresponding segment descriptor (and

the address is not translated by the BAT mechanism), the access maps to memory space and

page address translation is performed.

After a memory segment is selected, the processor creates the virtual address for the

segment and searches for the PTE that dictates the physical page number to be used for the

access. Note that I/O devices can be easily mapped into memory space and used as

memory-mapped I/O.

2.1 Address Translation Overview

The following sections provide a brief overview of the page and direct-store segment

address translation. For more information, refer to Chapter 7, “Memory Management,” in

The Programming Environments Manual.

2.1.1 Page Address Translation

The first step in page address translation for 64-bit implementations is the conversion of the

64-bit effective address of an access into the 80-bit virtual address. The virtual address is

then used to locate the PTE in the page tables in memory. The physical page number is then

extracted from the PTE and used in the formation of the physical address of the access.

The translation of an effective address to a physical address for 64-bit implementations is

described briefly:

• Bits 0–35 of the effective address comprise the effective segment ID used to select

a segment descriptor, from which the virtual segment ID (VSID) is extracted.

• Bits 36–51 of the effective address correspond to the page number within the

segment; these are concatenated with the VSID from the segment descriptor to form

the virtual page number (VPN). The VPN is used to search for the PTE in either an

on-chip TLB or the page table. The PTE then provides the physical page number

(RPN).

• Bits 52–63 of the effective address are the byte offset within the page; these are

concatenated with the RPN field of a PTE to form the physical address used to

access memory.

Table 20. Segment Descriptor Types

Segment Descriptor

T Bit

Segment Type

0 Memory segment

1 Direct-store segment

30 PowerPC Microprocessor Family: The Programmer’s Reference Guide

The translation of effective addresses to physical addresses for 32-bit implementations is

similar to that for 64-bit implementations, except that 32-bit implementations index into an

array of 16 segment registers instead of segment tables in memory to locate the segment

descriptor, and the address ranges are obviously different. Thus, the address translation is

as follows:

• Bits 0–3 of the effective address comprise the segment register number used to

select a segment descriptor, from which the virtual segment ID (VSID) is extracted.

• Bits 4–19 of the effective address correspond to the page number within the

segment; these are concatenated with the VSID from the segment descriptor to form

the virtual page number (VPN). The VPN is used to search for the PTE in either an

on-chip TLB or the page table. The PTE then provides the physical page number

(RPN).

• Bits 20–31 of the effective address are the byte offset within the page; these are

concatenated with the RPN field of a PTE to form the physical address used to

access memory.

2.1.2 Direct-Store Segment Address Translation

As described for memory segments, all accesses generated by the processor (with

translation enabled) that do not map to a BAT area, map to a segment descriptor. If T = 1

for the selected segment descriptor, the access maps to the direct-store interface, invoking

a specific bus protocol for accessing some special-purpose I/O devices. Direct-store

segments are provided for POWER compatibility. As the direct-store interface is present

only for compatibility with existing I/O devices that used this interface and the direct-store

interface protocol is not optimized for performance, its use is discouraged. Applications

that require low-latency load/store access to external address space should use memory-

mapped I/O, rather than the direct-store interface.

2.2 Segment Descriptor Definitions

The format of the segment descriptors is different for 64-bit and 32-bit implementations.

Additionally, the fields in the segment descriptors are interpreted differently depending on

the value of the T bit within the descriptor. When T = 1, the segment descriptor defines a

direct-store segment.

2.2.1 STE Format—64-Bit Implementations

In 64-bit implementations, the segment descriptors reside as segment table entries (STEs)

in hashed segment tables in memory. These STEs are generated and placed in segment

tables in memory by the operating system. Each STE is a 128-bit entity (two double words)

that maps one effective segment ID to one virtual segment ID. Information in the STE

controls the segment table search process and provides input to the memory protection

PowerPC Microprocessor Family: The Programmer’s Reference Guide 31

mechanism. Figure 25 shows the format of both double words that comprise a T = 0

segment descriptor (or STE) in a 64-bit implementation.

Figure 25. STE Format—64-Bit Implementations

Table 21 lists the bit definitions for each double word in an STE.

The Ks and Kp bits partially define the access protection for the pages within the segment.

The virtual segment ID field is used as the high-order bits of the virtual page number

(VPN).

The segment descriptors are programmed by the operating system and placed into segment

tables in memory, although some processors may additionally have on-chip segment

lookaside buffers (SLBs). These SLBs store copies of recently-used STEs that can be

accessed quickly, providing increased overall performance.

2.2.1.1 Address Space Register (ASR)

The ASR contains the control information for the segment table structure in that it defines

the highest order bits for the physical base address of the segment table. The format of the

Table 21. STE Bit Definitions for Page Address Translation—64-Bit

Implementations

Double

Word

Bit Name Description

0 0–35 ESID Effective segment ID

36–55 — Reserved

56 V Entry valid (V = 1) or invalid (V = 0)

57 T T = 0 selects this format

58 Ks Supervisor-state protection key

59 Kp User-state protection key

60 N No-execute protection bit

61–63 — Reserved

1 0–51 VSID Virtual segment ID

52–63 — Reserved

Reserved

0 3536 55565758596061 63

0515263

ESID 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 V T Ks Kp N 0 0 0

VSID 0 0 0 0 0 0 0 0 0 0 0

32 PowerPC Microprocessor Family: The Programmer’s Reference Guide

ASR is shown in Figure 26. The ASR contains bits 0–51 of the 64-bit physical base address

of the segment table. Bits 52–56 of the STEG address are derived from the hashing

function, (and bits 57–63 are zero at the beginning of a segment table search operation to

point to the beginning of an STEG). Therefore, the beginning of the segment table lies on

a 2

12

byte (4 Kbyte) boundary.

Note that unless all accesses to be performed by the processor can be translated by the BAT

mechanism when address translation is enabled (MSR[DR] or MSR[IR] = 1), the ASR must

point to a valid segment table. If the processor does not support 64 bits of physical address,

software should write zeros to those unsupported bits in the ASR. Otherwise, a machine

check exception can occur.

Additionally, values x0, 0x1000, and 0x2000 should not be used as segment table addresses

as they correspond to areas of the exception vector table reserved for implementation-

specific purposes.

Figure 26. ASR Register Format—64-Bit Implementations Only

2.2.2 Segment Descriptor Format—32-Bit Implementations

In 32-bit implementations, the segment descriptors are 32-bits long and reside in one of 16

segment registers. Figure 27 shows the format of a segment register used in page address

translation (T = 0) in a 32-bit implementation.

Figure 27. Segment Register Format for Page Address Translation—32-Bit

Implementations

Table 22 provides the corresponding bit definitions of the segment register in 32-bit

implementations.

0 51 52 63

Physical Address of Segment Table 0 0 0 0 0 0 0 0 0 0 0 0

Reserved

01234 78 31

T Ks Kp N 0 0 0 0 VSID

Reserved

PowerPC Microprocessor Family: The Programmer’s Reference Guide 33

The Ks and Kp bits partially define the access protection for the pages within the segment.

The virtual segment ID field is used as the high-order bits of the virtual page number

(VPN).

The segment register instructions are summarized in Table 23. These instructions are

privileged in that they are executable only while operating in supervisor mode.

2.2.3 Segment Descriptors for Direct-Store Segments

The format of many of the fields in the segment descriptors depends on the value of the

T bit. Figure 28 shows the format of segment descriptors (residing as STEs in segment

tables) that define direct-store segments for 64-bit implementations (T bit is set).

Table 22. Segment Register Bit Definition for Page Address Translation—32-Bit

Implementations

Bit Name Description

0 T T = 0 selects this format

1

Ks

Supervisor-state protection key

2

Kp

User-state protection key

3 N No-execute protection bit

4–7 — Reserved

8–31 VSID Virtual segment ID

Table 23. Segment Register Instructions—32-Bit Implementations Only

Instruction Description

mtsr SR,rS Move to Segment Register

SR[SR]← rS

mtsrin rS,rB Move to Segment Register Indirect

SR[rB[0–3]]←rS

mfsr rD,SR Move from Segment Register

rD←SR[SR]

mfsrin rD,rB Move from Segment Register Indirect

rD←SR[rB[0–3]]

34 PowerPC Microprocessor Family: The Programmer’s Reference Guide

Figure 28. Segment Descriptor Format for Direct-Store Segments—64-Bit

Implementations

Table 24 shows the bit definitions for the segment descriptors when the T bit is set for 64-

bit implementations.

In 32-bit implementations, the segment descriptors reside in one of 16 segment registers.

Figure 29 shows the register format for the segment registers when the T bit is set for 32-

bit implementations.

Figure 29. Segment Register Format for Direct-Store Segments—32-Bit

Implementations

Table 24. Segment Descriptor Bit Definitions for Direct-Store Segments—64-Bit

Implementations

Double Word Bit Name Description

0 0–35 ESID Effective segment ID

36–55 — Reserved

56 V Entry valid (V = 1) or invalid (V = 0)

57 T T = 0 selects this format

58 Ks Supervisor-state protection key

59 Kp User-state protection key

61–63 — Reserved

1 0–63 — Device specific data for I/O controller

Reserved

0 3536 555657585960 63

0 63

Controller-Specific Information

ESID 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 V T Ks Kp 0 0 0 0

Double Word 0

Double Word 1

T Ks Kp BUID Controller-Specific Information

0 1 2 3 11 12 31

PowerPC Microprocessor Family: The Programmer’s Reference Guide 35

Table 25 shows the bit definitions for the segment registers when the T bit is set for 32-bit

implementations.

2.3 Page Table Entry (PTE) Definitions

Page table entries (PTEs) are generated and placed in page tables in memory by the

operating system. The PowerPC OEA defines similar PTE formats for both 64- and 32-bit

implementations in that the same fields are defined. However, 64-bit implementations

define PTEs that are 128 bits in length while 32-bit implementations define PTEs that are

64 bits in length. Additionally, care must be taken when programming for both 64 and 32-

bit implementations, as the bit placements of some fields are different. Some of the fields

are defined as follows:

• The virtual segment ID field corresponds to the high-order bits of the virtual page

number (VPN), and, along with the H, V, and API fields, it is used to locate the PTE

(used as match criteria in comparing the PTE with the segment information).

• The R and C bits maintain history information for the page.

• The WIMG bits define the memory/cache control mode for accesses to the page.

• The PP bits define the remaining access protection constraints for the page.

Conceptually, the page table in memory must be searched to translate the address of every

reference.

2.3.1 PTE Format for 64-Bit Implementations

In 64-bit implementations, each PTE is a 128-bit entity (two double words) that maps a

virtual page number (VPN) to a physical page number (RPN). Information in the PTE is

used in the page table search process (to determine a page table hit) and provides input to

Table 25. Segment Register Bit Definitions for Direct-Store Segments

Bit Name Description

0 T T = 1 selects this format.

1 Ks Supervisor-state protection key

2 Kp User-state protection key

3–11 BUID Bus unit ID

12–31 — Device specific data for I/O controller

36 PowerPC Microprocessor Family: The Programmer’s Reference Guide

the memory protection mechanism. Figure 30 shows the format of the two double words

that comprise a PTE for 64-bit implementations.

Figure 30. Page Table Entry Format—64-Bit Implementations

Table 26 lists the corresponding bit definitions for each double word in a PTE as defined

above.

The PTE contains an abbreviated page index rather than the complete page index field

because at least 11 of the low-order bits of the page index are used in the hash function to

select a PTE group (PTEG) address (PTEG addresses define the location of a PTE).

Therefore, these 11 lower-order bits are not repeated in the PTEs of that PTEG.

Table 26. PTE Bit Definitions—64-Bit Implementations

Double

Word

Bit Name Description

0 0–51 VSID Virtual segment ID—corresponds to

the high-order bits of the virtual page

number (VPN)

52–56 API Abbreviated page index

57–61 — Reserved

62 H Hash function identifier

63 V Entry valid (V = 1) or invalid (V = 0)

1 0–51 RPN Physical page number

52–54 — Reserved

55 R Referenced bit

56 C Changed bit

57–60 WIMG Memory/cache access control bits

61 — Reserved

62–63 PP Page protection bits

Reserved

051525455565760616263

051525657616263

RPN 0 0 0 R C WIMG 0 PP

VSID API 0 0 0 0 0 H V

PowerPC Microprocessor Family: The Programmer’s Reference Guide 37